Verilog 파일을 실행하기 위해서는 모델심(ModelSim) 프로그램을 이용한다.

모델심 프로그램을 실행하면 위와 같은 창이 화면에 뜬다. 그렇다면 모델심이 열리고 있다는 뜻이다.

모델심 초기화면

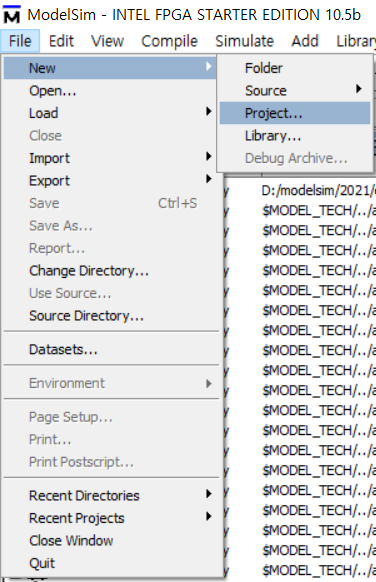

모델심을 열면 다음과 같이 화면이 뜬다. 여기서 Verilog 파일을 실행하기 위해서는 프로젝트를 만들어야 한다.

그래서 이번 시간에는 프로젝트를 생성하는 방법에 대해서 알아보려 한다.

1. Creat Project

[File] - [New] - [Project...]를 통해 프로젝트를 생성한다.

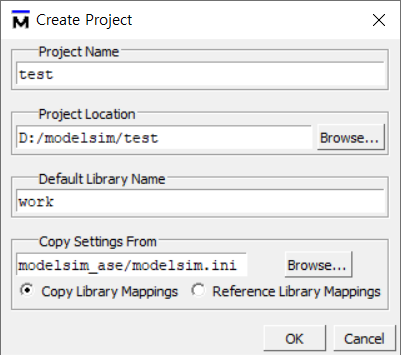

다음과 같이 Create Project 창이 화면에 뜬다.

프로젝트 이름(Project Name)을 입력하고, 프로젝트 경로를 원하는 곳(Project Loaction)으로 변경하면 된다.

경로를 변경하지 않아도 상관없지만, 나중에 프로젝트를 편하게 찾아보기 위해 변경하여 사용한다.

※ 프로젝트 생성 시 주의할 점!

프로젝트 폴더명과 프로젝트 이름은 동일해야 한다.

※ 프로젝트 이름 설정 시 주의할 점!

프로젝트 이름을 설정할 때 주의할 점이 여러 가지 있는데, 추후에 관련 글을 쓰도록 하겠다.

만약 test라는 프로젝트를 만들고 싶다면 다음과 같이 설정한다.

프로젝트 이름: test

프로젝트 경로: D:/modelsim/test

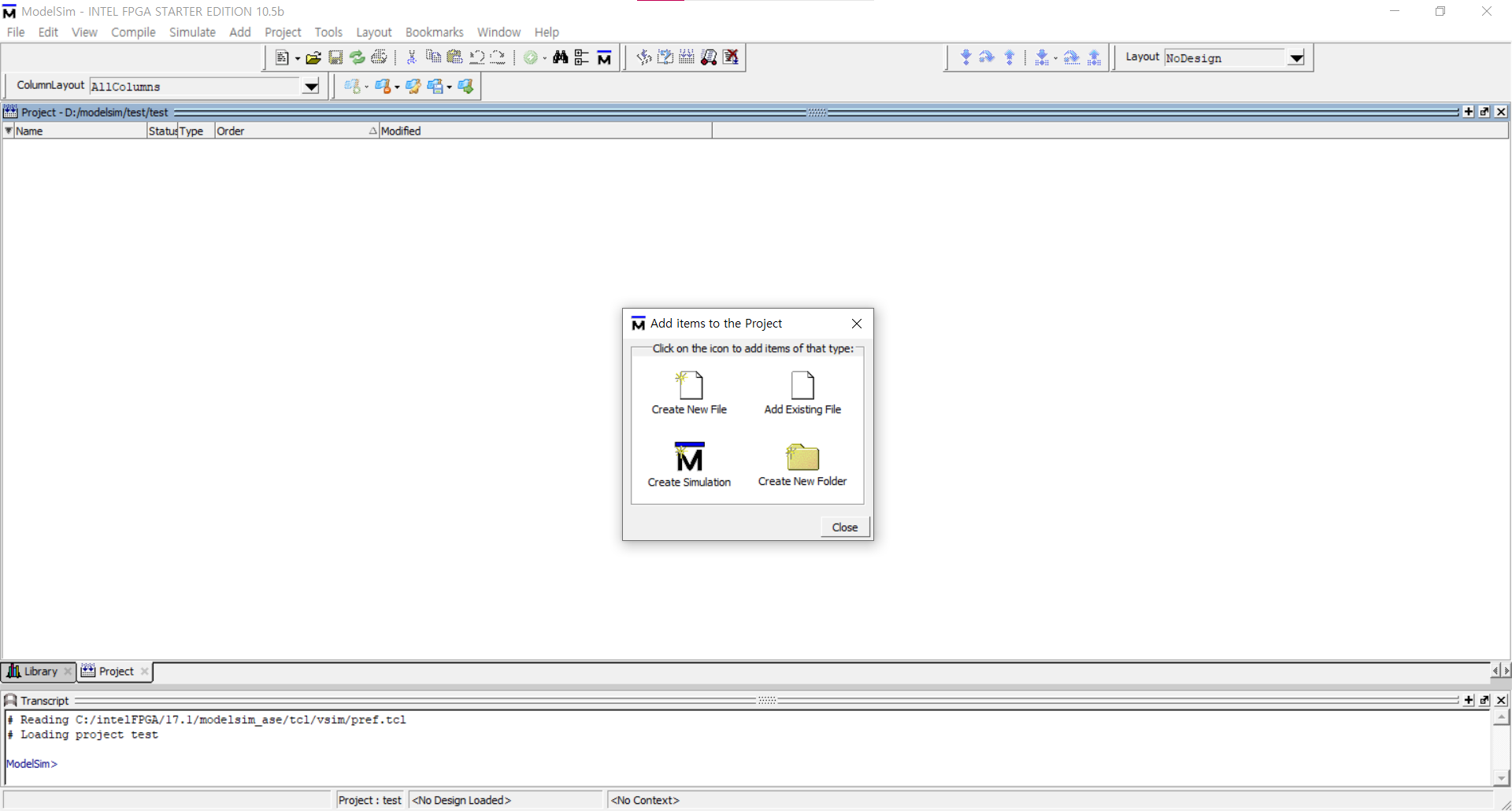

2. Add items to the Project

Create Project 창에서 OK 버튼을 누르면 다음과 같이 화면이 넘어가면서 Add items to the Project라는 창이 뜬다.

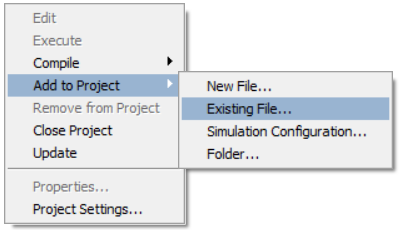

만약 Add items to the Project 창이 사라졌어도 걱정하지 않아도 된다.

빈 화면에 [오른쪽 마우스] - [Add to Project]를 통해 파일을 생성할 수 있다.

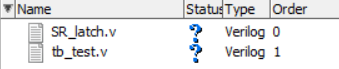

tb_test.v 와 SR_latch.v라는 새로운 파일을 만들 것이다.

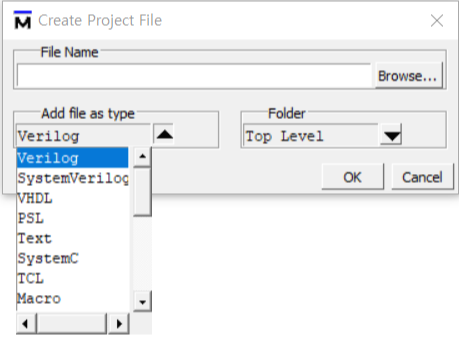

Create New File을 선택하면 Create Project File 창이 뜬다.

파일명을 tb_test와 SR_latch로 입력한다. (File Name)

Verilog HDL 코드를 작성할 것이기 때문에 파일 형식을 Verilog로 변경한다. (Add file as type)

만약, 미리 만들어둔 파일이 있다면 해당 파일을 사용하면 된다.

--> Add Existing File을 누른 후 해당 창에서 Browse... 를 통해 파일 선택

3. Edit File

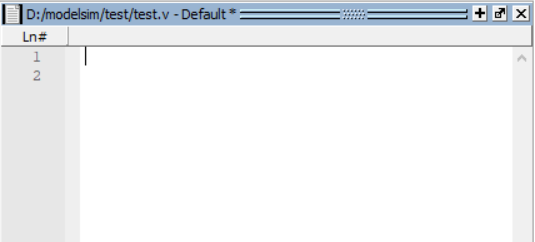

아무것도 입력이 안된 파일이 생성된다.

해당 파일을 더블 클릭하거나, 오른쪽 마우스를 눌러 Edit 버튼을 누르면 파일을 수정할 수 있는 창이 뜨게 된다.

해당 창에서 입력해도 무방하나, 나는 해당 창이 불편해서 vim 창을 열어 사용한다. 이것은 개인 차이로 편한 프로그램을 이용하면 된다.

해당 화면에 코드를 채워나가면 된다.

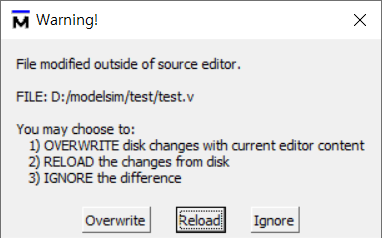

Warning! File modified outside of source editor.

modelsim의 편집창이 아닌 다른 프로그램을 통해 코드를 작성하면 다음과 같은 창이 뜬다.

여기서 Reload 버튼을 누르면 수정한 코드 내용이 반영되므로 Reload 버튼을 눌러야 한다.

다른 버튼을 누르면 수정된 코드 내용이 반영되지 않는다!!

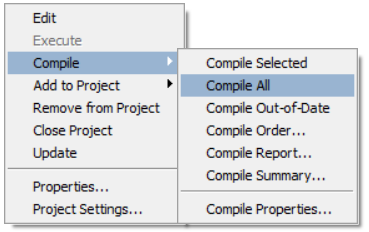

4. Compile

컴파일을 (한꺼번에) 하는 방법은 2가지가 있다.

1. 다음 아이콘 선택(Compile All)

2. [오른쪽 마우스] - [Compile] - [Compile All]

컴파일에 성공하면 다음과 같이 변하는 것을 볼 수 있다.

컴파일에 실패하였다면 빨간색으로 Error가 뜨는 부분을 더블클릭하면 자세한 에러 내용을 볼 수 있다.

5. Simulate

시뮬레이션을 하기 위해 위의 화면에서 빨간색 네모 박스로 표시된 버튼을 누르면 Start Simulation 창이 뜬다.

여기서 work에 위치한 tb_test를 선택하고 OK 버튼을 누른다.

tb_test는 테스트벤치(testbench) 또는 스티뮬러스(stimulus)라고 한다.

이는 회로를 검증하기 위한 시뮬레이션을 수행한다.

쉽게 설명하자면, C언어의 main 함수라고 볼 수 있다.

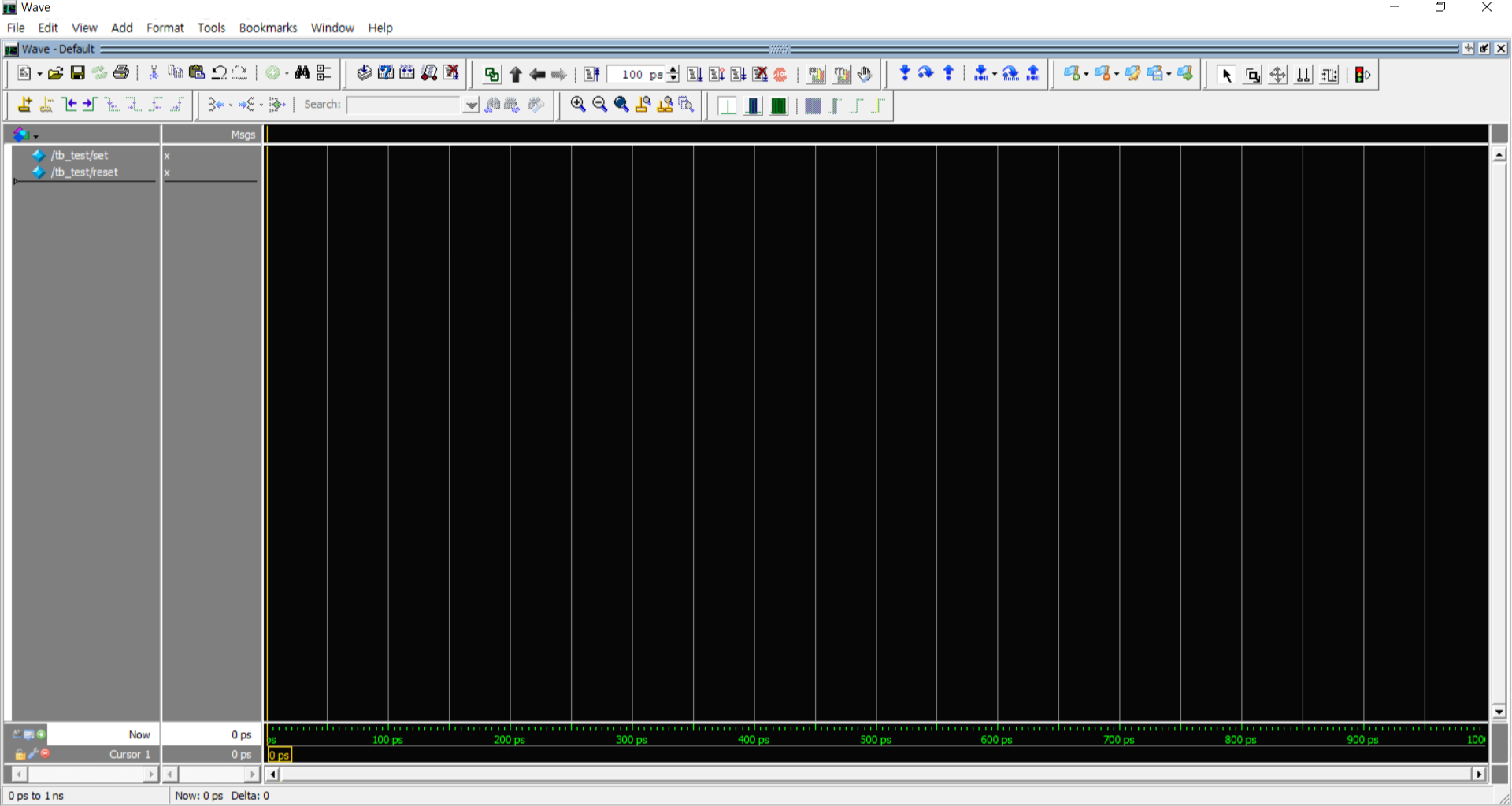

6. Add to Wave

간단하게 파형을 추가하는 방법은 다음과 같이 2가지가 있다.

1. [오른쪽 마우스] - [Add Wave] 클릭

2. 단축키 Ctrl + W 사용

만약, 모든 요소의 파형을 보고 싶다면

--> [오른쪽 마우스] - [Add to] - [Wave] - [All items in design]

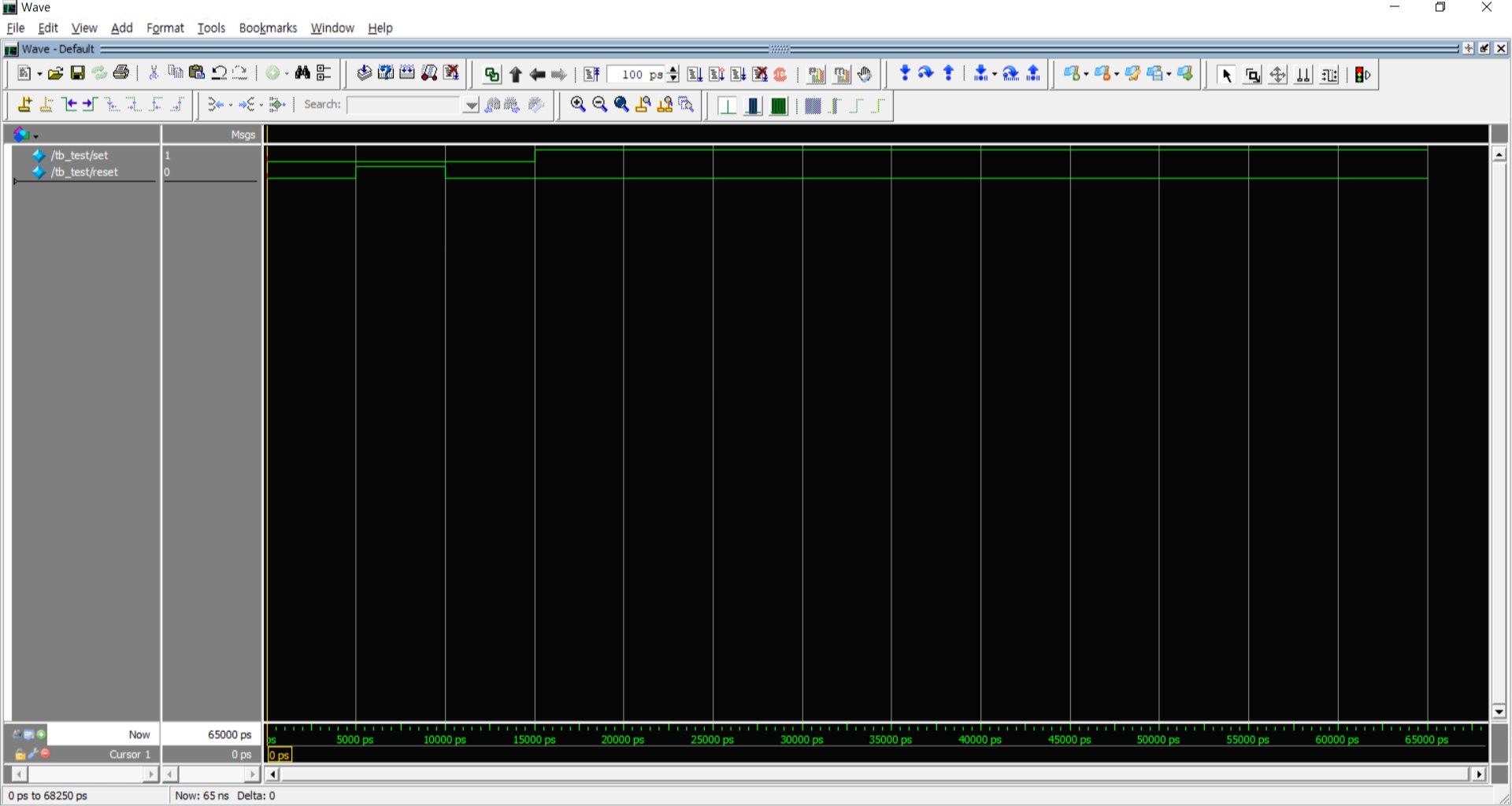

Add to Wave를 실행한 초기 화면이다.

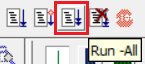

7. Run

Wave 창에서 실행되는 파형을 보기 위해서는 Run을 해야 한다.

모든 wave를 실행하기 위해서 Run -All 버튼을 누른다.

Are you sure you want to finish?

Run 버튼을 누르면 Finish Vsim 창이 뜨는데, 아니요(N)를 눌러야 한다!!

예(Y)를 누르면 Wave 창이 종료된다!!

Wave 창에 다음과 같이 파형이 생성된 것을 볼 수 있다.

그러나, 화면에 모든 파형이 보이지 않아 보기 어렵다.

Zoom Full(F) 버튼을 누르거나, 단축키 Shift + F를 누르면 아래와 같이 한 화면에 모든 파형을 볼 수 있다.

이번 글에서는 프로젝트를 생성하는 방법에 대해서 알아보았다.

다음 글에서는 간단히 프로젝트를 생성하는 것을 넘어서 이번 글에서의 과정을 빠르게 쉽게 실행할 수 있는 방법에 대해서 알아보려 한다.

'Verilog HDL' 카테고리의 다른 글

| 순차회로와 FSM (0) | 2021.08.23 |

|---|---|

| [조합회로] 4비트 전가산기 설계하기 (0) | 2021.07.28 |

| [조합회로] 4:1 멀티플렉서 설계하기 (0) | 2021.07.28 |

| [ModelSim] Verilog 조합회로 설계 방법 (0) | 2021.07.28 |

| [ModelSim] 컴파일 및 시뮬레이션 자동화 방법 (0) | 2021.07.27 |

![[ModelSim] 프로젝트 생성 및 실행 방법](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdna%2FkJIKu%2FbtracOJoxOK%2FAAAAAAAAAAAAAAAAAAAAACD9k84p9fduKmFVfmui0hTTGFGkDg8d-DJPjBKYwLsT%2Fimg.png%3Fcredential%3DyqXZFxpELC7KVnFOS48ylbz2pIh7yKj8%26expires%3D1769871599%26allow_ip%3D%26allow_referer%3D%26signature%3DDKrrRUxWfWFW32SCKLFvVEOnVUc%253D)